# Enhanced Vote Count Circuit based on NOR Flash **Memory for Fast Similarity Search**

Haiyan Shu, Wenyu Jiang, Xiaoming Bao, Huan Zhou, and Rongshan Yu Institute for Infocomm Research, A\*STAR, Singapore

## **Vote Count Circuits**

### Vote Count concept

- Both reference vectors (v<sub>i</sub> for j-th vector) and the query vector (q) are converted into discrete vectors by some deterministic hashing;

- let f<sub>t</sub>(v) denote a vector v's value at hashed dimension i

- let c<sub>i</sub> denote a counter associated with vector v<sub>i</sub>, initialize to 0

$$\begin{array}{l} \text{for (i = 0; i < L; i++)} \\ \forall v_j, if \left(f_i\!\left(v_j\right) == f_i\!\left(q\right)\right) c_j + +; \\ \forall \ v_j, \text{return} \ v_j \text{ as candidates} \ if c_j \geq T; \end{array}$$

#### Vote Count Circuits

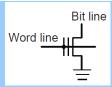

> Exploiting the fact that when reading a word on a row, its corresponding word-line (WL) will activate all cells on that row; by having a sense-amp at each column or bit-line (BL), the entire row is read out in 1 access cycle;

#### Enhanced Vote Count (EVC)

- Comparing m values instead of 1 (bet, query and reference) at a time;

- This simultaneous m-value comparison made possible by using the interlocked design, where 2 cells are used to represent 1 pattern bit. First proposed for NAND Flash, now also proposed for NOR Flash.

NOR flash memory

## Prototype chip

- Customized 0.18um NOR Flash circuit, 1024 word-lines and 1024 bit-lines which can accommodate 1024 reference vectors to be retrieved simultaneously

- Each hashing feature vector may have up to 512 dimensions.

- Retained the mux that shares each sense-amplifier with 32 columns.

- > A test PCB is designed to mount the EVC prototype chip, and integrate with an FPGA development board

### VC and EVC comparison L=512, m=8

# Performance Analysis

ote Count Chip and Board

#### Speed and power consumption

|                             | DRAM implementation | NAND implementation           | NOR implementation            |

|-----------------------------|---------------------|-------------------------------|-------------------------------|

| original vote count circuit | $L \cdot 	au_{par}$ | $L \cdot \tau_{ser}$          | $L \cdot 	au_{par}$           |

| EVC circuit                 |                     | $\frac{L}{m} \cdot 	au_{ser}$ | $\frac{L}{m} \cdot 	au_{par}$ |

$\tau_{par}$ : 25 – 50ns  $\tau_{ser}$ : 5 – 50 $\mu$ s L: # of hashed dimensions m: # of values simultaneously compared in EVC Competitive Analysis with Commercial Software and Open Source Toolkits

| Performance Metrics (1 Million DB | EVC                |                       | Open Source Toolkits |

|-----------------------------------|--------------------|-----------------------|----------------------|

| items, find top-100 matches)      | low-density        | high-density          | Multi-index Hashing  |

| Search Speed                      | 0.139ms            | $6.5 \mu s$           | 3ms                  |

| Energy per Search                 | 0.75mJ             | 0.03mJ                | 150mJ                |

| Physical Space                    | $50cm^2 \cdot 1cm$ | $1 - 2cm^2 \cdot 1cm$ | desktop PC           |