# **REDUCED-COMPLEXITY TRELLIS MIN-MAX DECODER FOR NON-BINARY LDPC CODES**

### Abstract

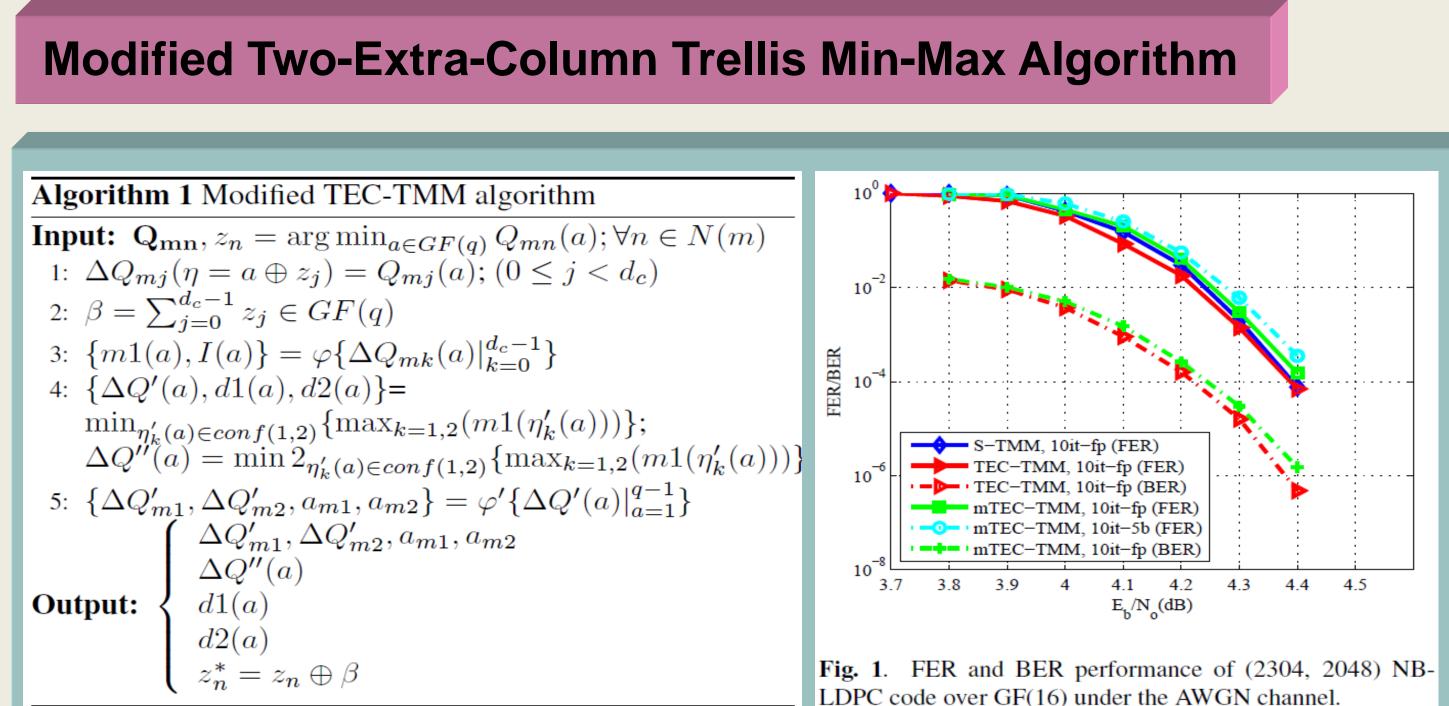

- A novel modified TEC-TMM algorithm and decoder architecture are proposed.

- Exchanged messages between CNU and VNU are significantly reduced.

- A layered decoder for (2304, 2048) NB-LDPC code over GF(16) is designed.

- Area reductions for CNU and whole decoder are 19.4% and 26.56%, respectively, with similar FER performance.

### Introduction

- NB-LDPC codes outperform their binary counterparts in terms of error correction performance.

- Decoder architectures, especially CNU, have high complexity and large memory requirement.

- New algorithm and architectures are required to reduce the decoder area and improve the throughput.

- Two extra columns,  $\Delta Q'$  and  $\Delta Q''$ , including q elements are constructed based on only the first minimum values in each row.

- Only two elements with the smallest values in the first extra column  $\Delta Q'$  are kept.

- The number of output elements is reduced.

- The remain  $\Delta Q'$  elements are approximately calculated as  $\Delta Q'(a) = \gamma \Delta Q'_{m2}$ .

## Huyen Pham Thi and Hanho Lee Dept. of Information and Communication Engr., Inha University, Korea

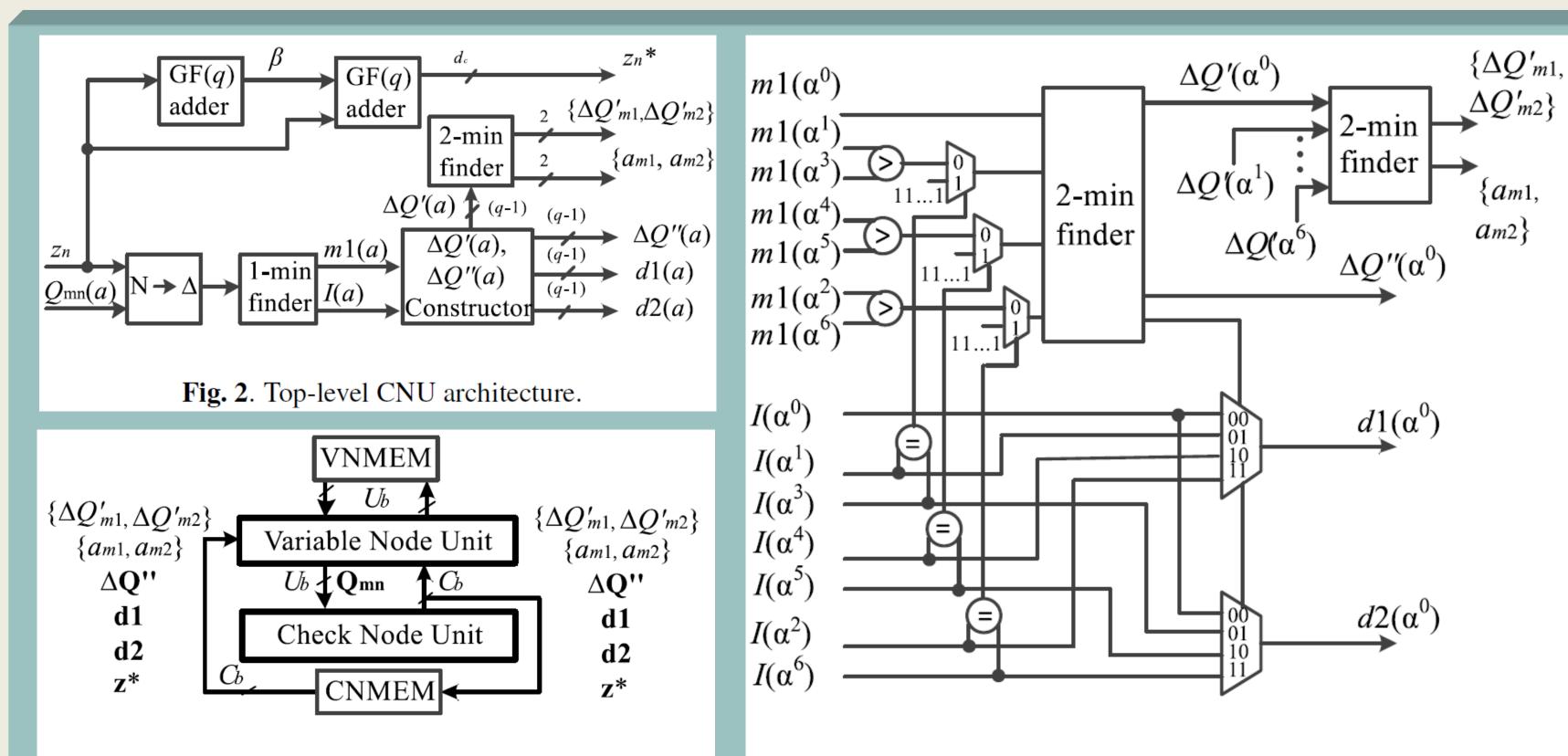

## **NB-LDPC** Decoder Architecture

Fig. 4. Top-level decoder architecture.

## **Experimental Results**

- Table 1 shows that the proposed CNU reduced count by 40.3% and exchanged bits compared to [6].

- Compared to [9], gate count and exchange reduced by 19.4% and 12%, respectively.

- compared to [6] and [9], respectively.

- improvement in the maximum frequency.

Contact information: <u>phamhuyenmta87@qmail.com</u>, <u>hhlee@inha.ac.kr</u>

- m1(a) finders.

- $\Delta Q'_{m2}$ .

- The architecture reduces because finder.

**Fig. 3**. Two extra column constructor for  $\alpha^0$  over GF(8).

| lucco acto  | Table 1. CNU       | J complex | kity comp | arison   | - |

|-------------|--------------------|-----------|-----------|----------|---|

| luces gate  | $GF(16), d_c = 36$ | [6]       | [9]       | Proposed |   |

| by 85.5%,   | Gate count (NAND)  | 80.2K     | 59.4K     | 47.86K   |   |

|             | Memory (bits)      | 2880      | 474       | 417      | - |

| ge bits are | Quantization       | 5         | 5         | 5        |   |

|             |                    |           |           |          | - |

• Table 2 shows that the proposed decoder greatly reduces gate count by 62% and 26.56%, • Reducing both the CNU complexity and wiring congestion between CNU and VNU leads to a great Overall efficiency of the proposed decoder is almost twice as high as the one of the decoder in [9].

| Table 2. Comparison of the proposed (2304, 2048) NB- |               |             |           |  |  |  |

|------------------------------------------------------|---------------|-------------|-----------|--|--|--|

| LDPC layered decoder over GF(16) with other works    |               |             |           |  |  |  |

| $GF(16), d_c = 36$                                   | [6]           | [9]         | Proposed  |  |  |  |

| Report                                               | Post-layout   | Post-layout | Synthesis |  |  |  |

| Technology                                           | 90-nm         | 90-nm       | 90-nm     |  |  |  |

| Quantization                                         | 5             | 5           | 5         |  |  |  |

| Gate count<br>(NAND)                                 | 1882 <b>K</b> | 975K        | 716K      |  |  |  |

| $f_{clk}$                                            | 330.8         | 333.3       | 433.8     |  |  |  |

| Throughput<br>(Mbps)                                 | 957.5         | 964.7       | 1396      |  |  |  |

| Efficiency<br>(Mbps/M gates)                         | 508.8         | 989.4       | 1949.7    |  |  |  |

• (q-1) 1-min finders with dc inputs are proposed to find the most reliable messages instead of 2-min

• Only one 2-min finder is proposed to find the first two minimum values  $\Delta Q'_{m1}$ ,

> CNU proposed significantly the complexity using 1-min of

• CNU area is greatly reduced when increasing dc value.