# A HIGH PERFORMANCE BASEBAND INSTRUMENT

Institution: UNIVERSITY OF CALIFORNIA, DAVIS

- Author: Jeremy W. Webb- jwwebb@ucdavis.edu

- Mentor: Bevan Baas bbaas@ucdavis.edu

- Project Date: March 2011 (Duration: 2 years)

- Project URL: http://msee.jwebb-design.com/measbd/

### A HIGH PERFORMANCE BASEBAND INSTRUMENT

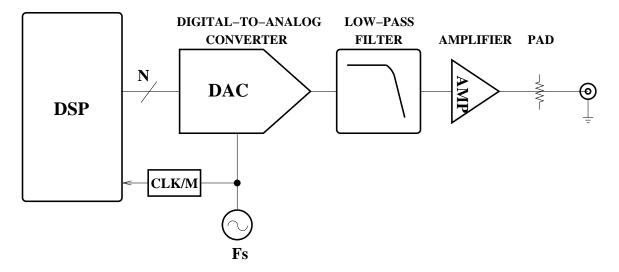

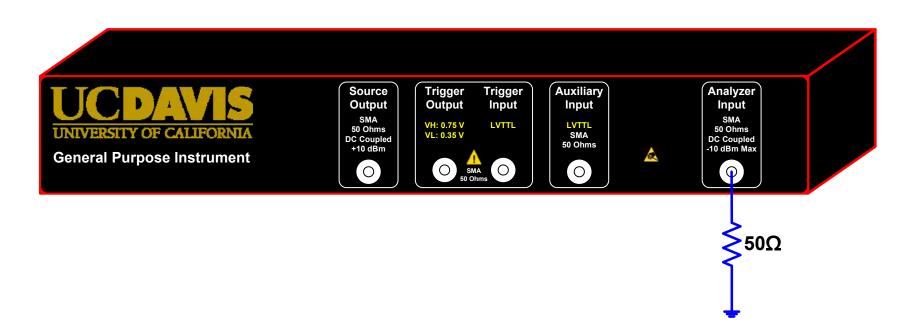

Testing complex digital signal processors (DSPs), such as the Asynchronous Array of Simple Processors (AsAP), requires a development platform with sufficient signal bandwidth and system performance to provide and consume data to and from the DSP. Without a development platform, verification of DSPs would be limited to monitoring test output signals for an indication of performance and successful operation. This document describes the design of a General Purpose Instrument which will simplify the testing and characterization of the AsAP processor when performing real world DSP tasks. The General Purpose Instrument is a flexible platform capable of targeting a wide variety of applications, such as signal generation and signal analysis.

### **Project Goals**

- $\bullet\,$  Signal generation and analysis frequency range from DC to 110  $\rm\,MHz.$

- A 334-processor platform with real-time I/O.

- Flexible waveform generation, loading, and capture.

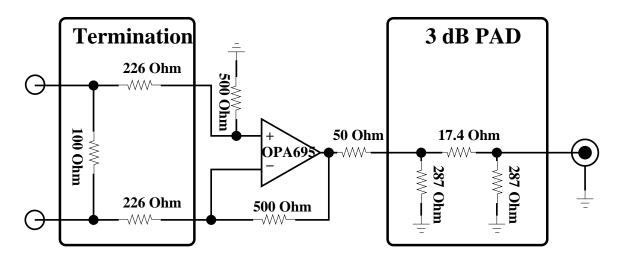

- A 50  $\Omega$  input and output impedance to simplify interconnection with standard test and measurement equipment.

### **Project Contributions**

- General Purpose Instrument system architecture design.

- Measurement board design, layout, and characterization.

- Data Path field programmable gate array (FPGA) system architecture design and SystemVerilog HDL development.

- Control FPGA embedded soft-core processor software architecture design.

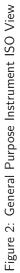

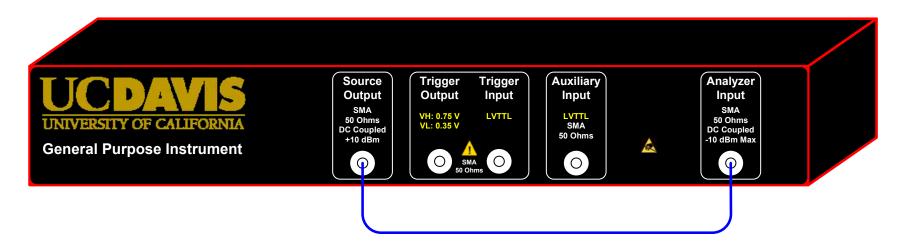

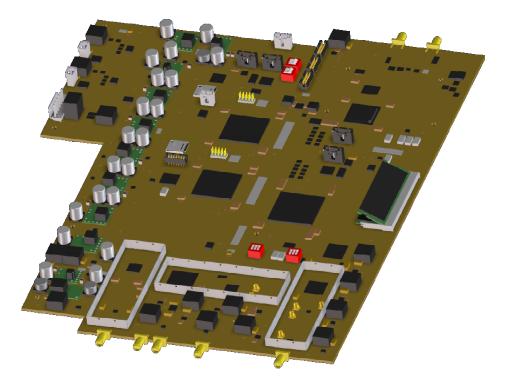

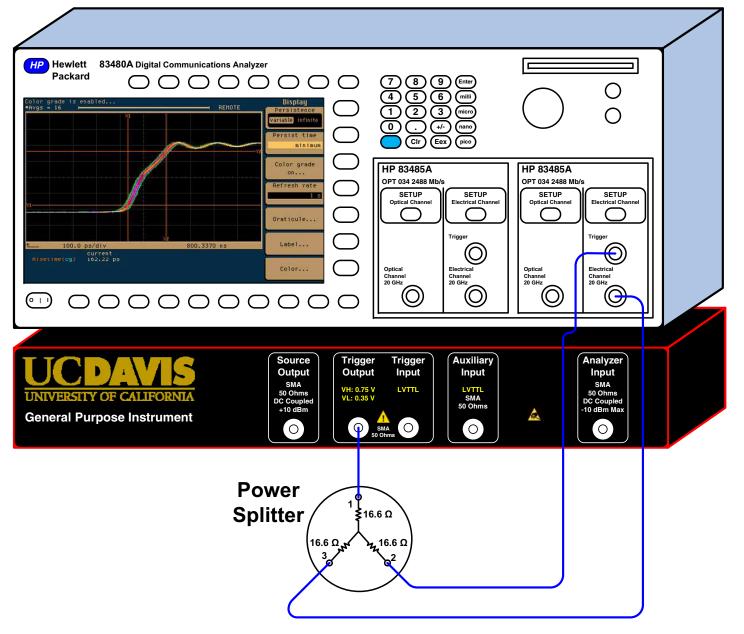

**Conclusion** The General Purpose Instrument, shown in Figures 1 and 2, is a successful development platform that can be used for a wide variety of AsAP DSP software prototyping. This platform can be used to target applications from software defined radios to cognitive radio. The signal bandwidth of the front end designs exceeded my initial design goals of a frequency range from DC to 110 MHz by 15 MHz.

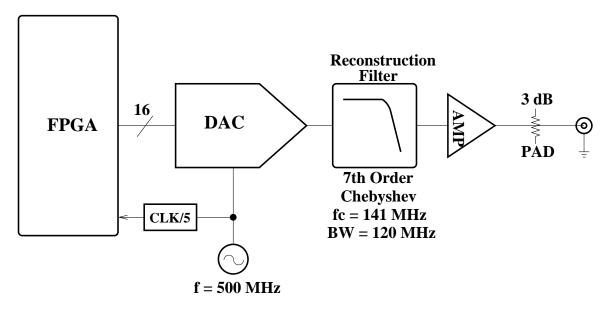

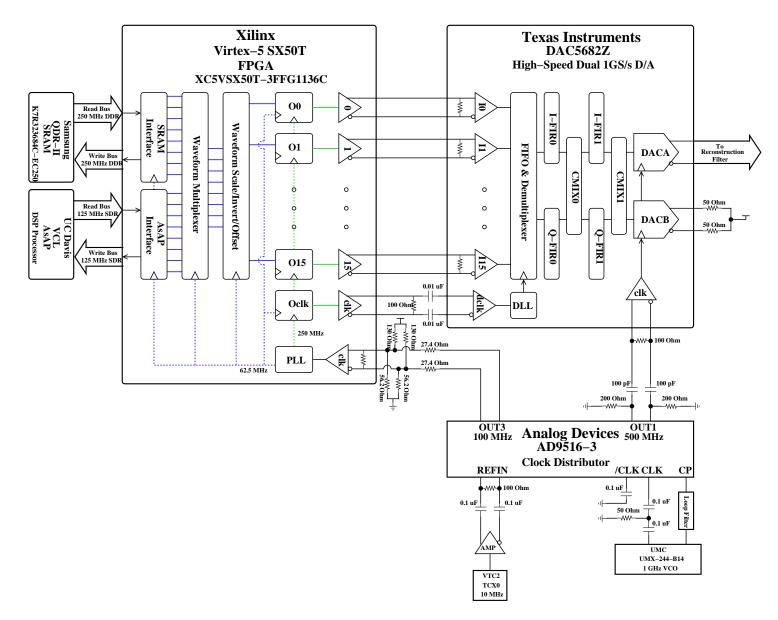

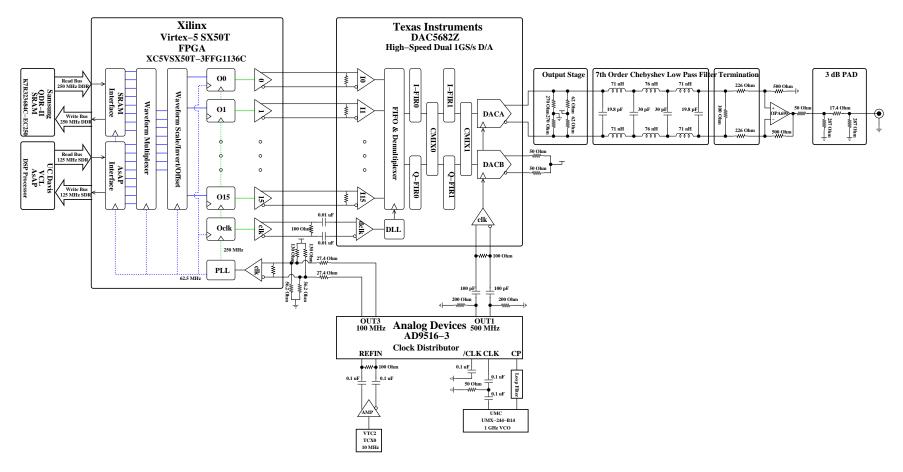

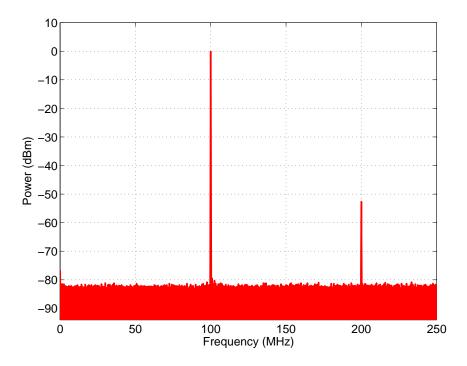

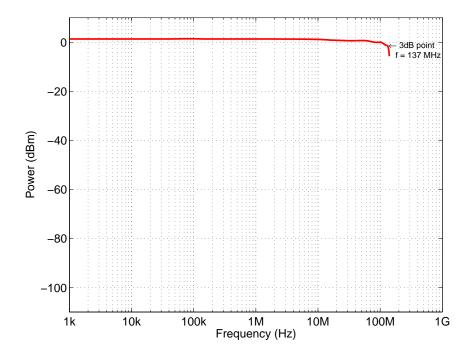

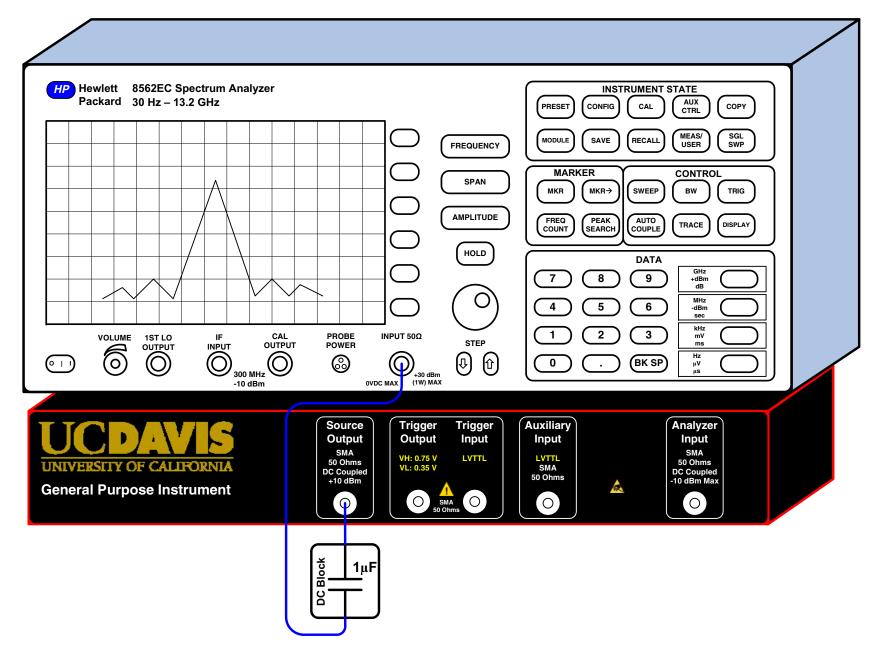

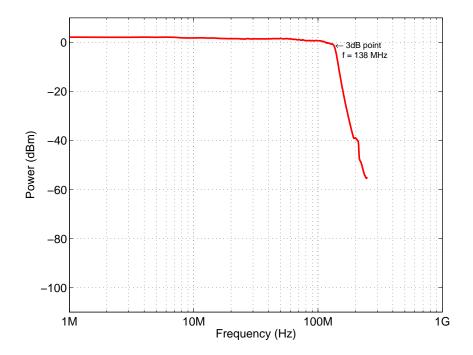

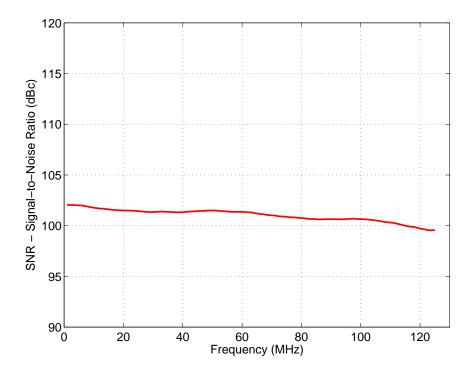

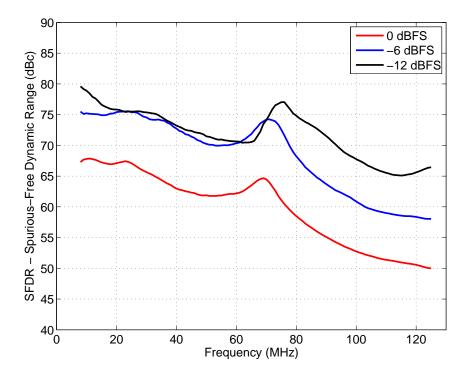

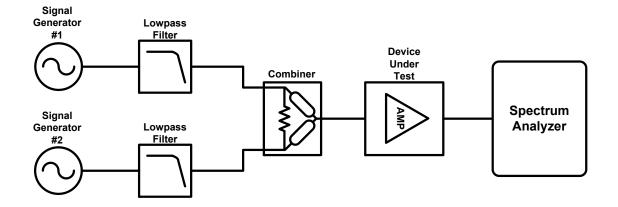

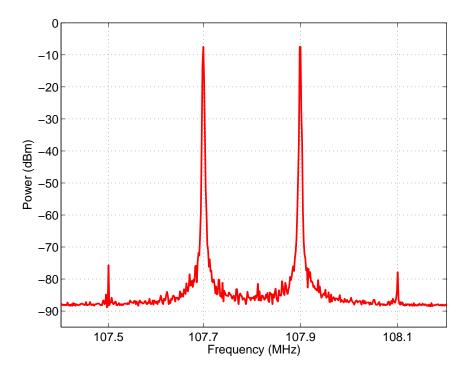

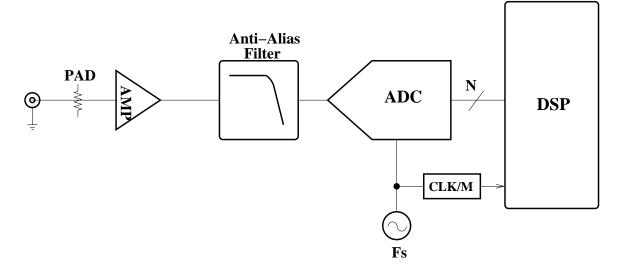

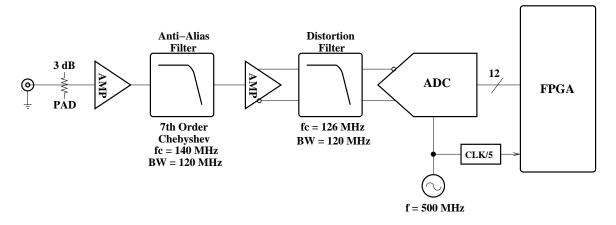

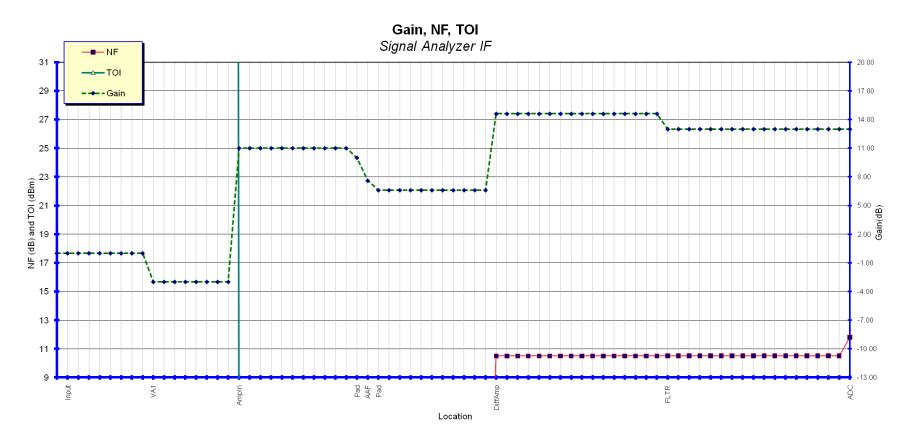

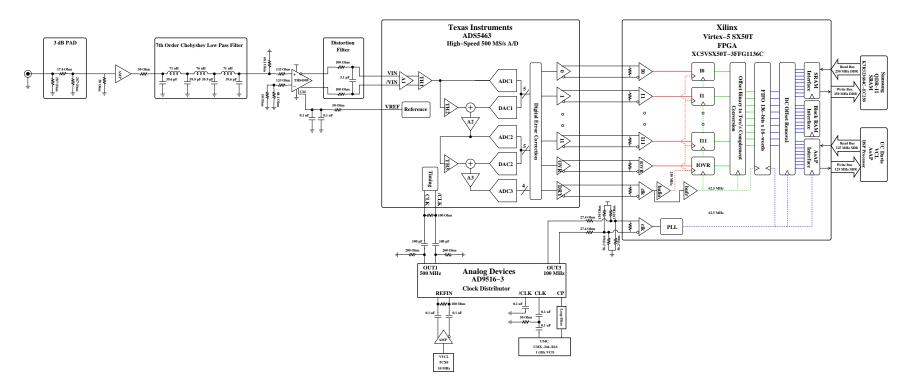

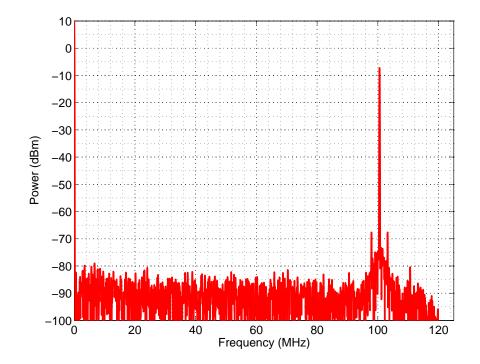

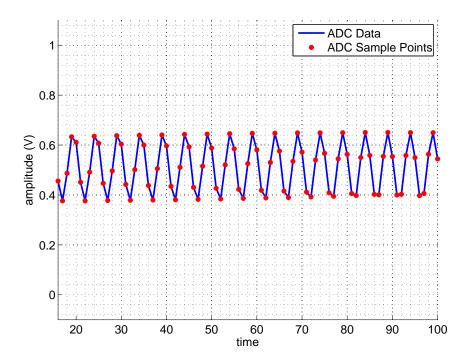

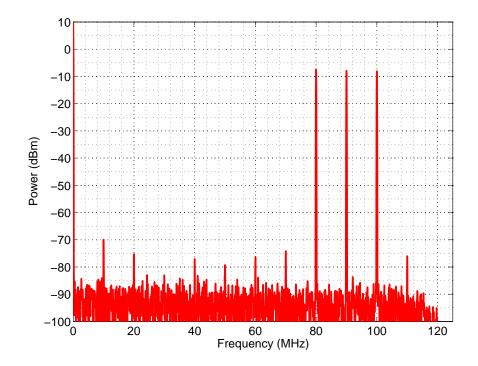

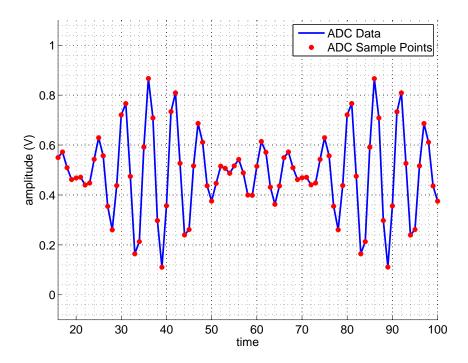

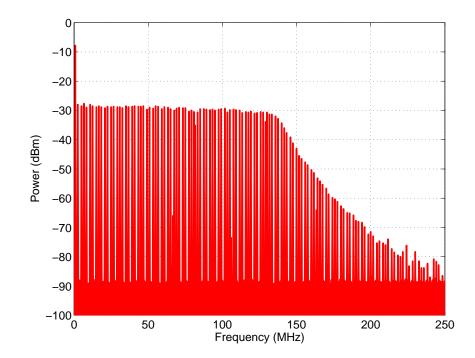

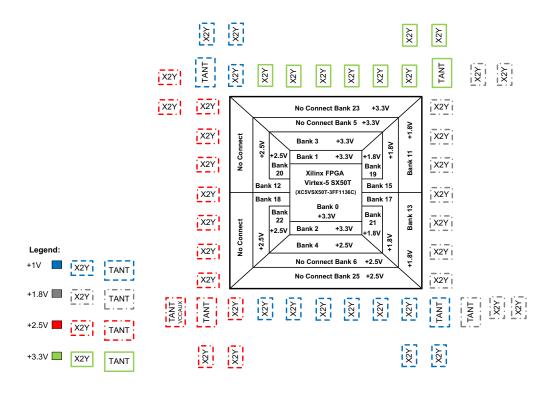

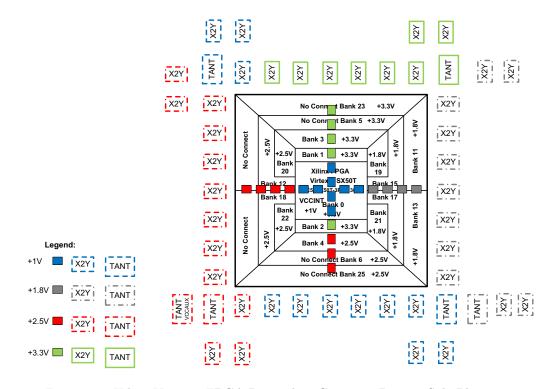

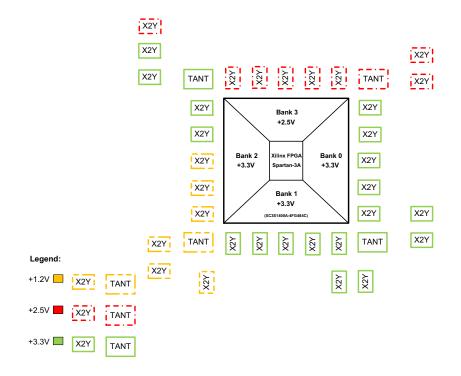

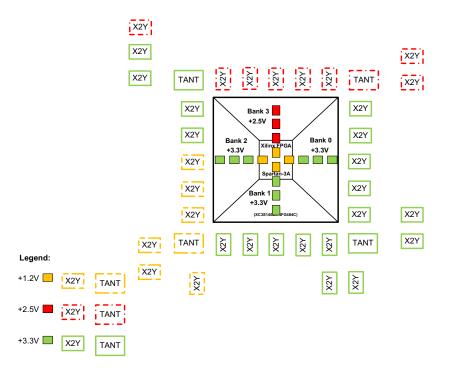

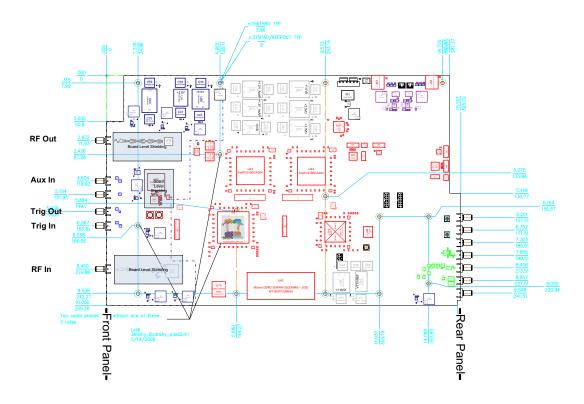

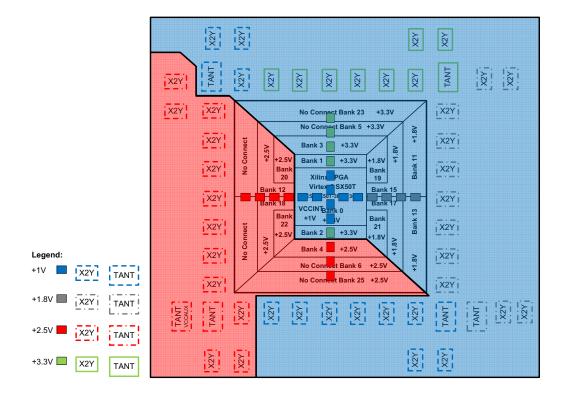

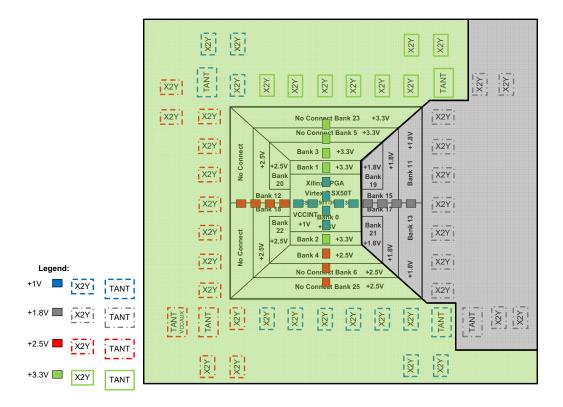

The General Purpose Instrument is a flexible platform capable of targeting a wide variety of applications, such as signal generation and signal analysis, and includes: a 12-bit, 500 MS/s analog-to-digital converter (ADC) input, a dual-channel, 16-bit, 1 GS/s digital-to-analog converter (DAC) output, a Xilinx Virtex-5 SX50T data path field programmable gate array (FPGA), a Xilinx Spartan-3A XC3S1400A control FPGA, a 36-Mbit QDR-II static random access memory (SRAM), a 2 GB DDR2 synchronous dynamic random access memory (SDRAM), a 512 Mbit DDR SDRAM, and two 2 GB microSD cards. The signal analyzer input operates with a -3 dB frequency of 138 MHz, a spurious-free dynamic range (SFDR) of 68.49 dBc at a power level of -6 dBFS, and a signal-to-noise ratio (SNR) of 101.02 dBc.

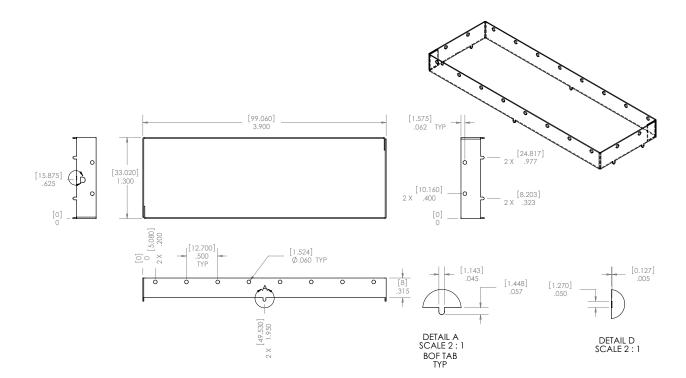

Figure 1: General Purpose Instrument ISO View with open top

Jeremy W. Webb

## A HIGH PERFORMANCE BASEBAND INSTRUMENT

By

JEREMY WILLIAM WEBB B.S. (University of California, Davis) December, 2000

### THESIS

Submitted in partial satisfaction of the requirements for the degree of

MASTER OF SCIENCE

$\mathrm{in}$

Electrical and Computer Engineering

in the

### OFFICE OF GRADUATE STUDIES

of the

### UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Bevan M. Baas, Chair

Gary E. Ford

Andre Knoesen

$\begin{array}{c} \text{Committee in charge} \\ 2011 \end{array}$

© Copyright by Jeremy William Webb 2011 All Rights Reserved

## Abstract

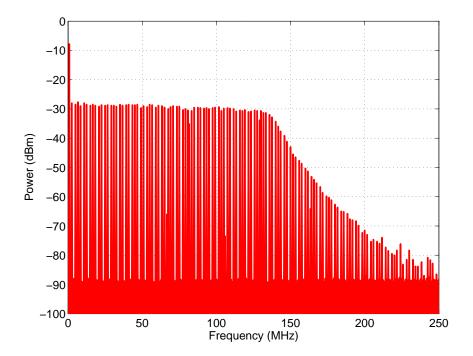

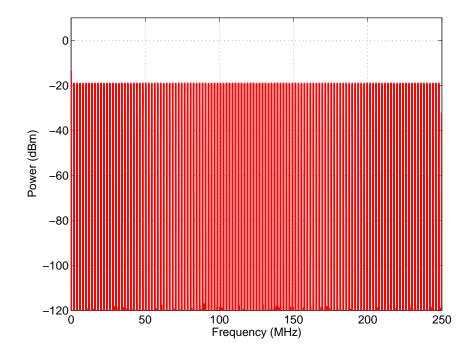

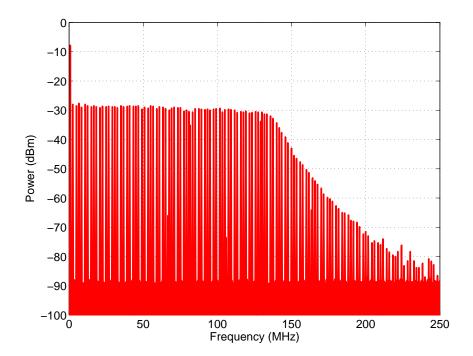

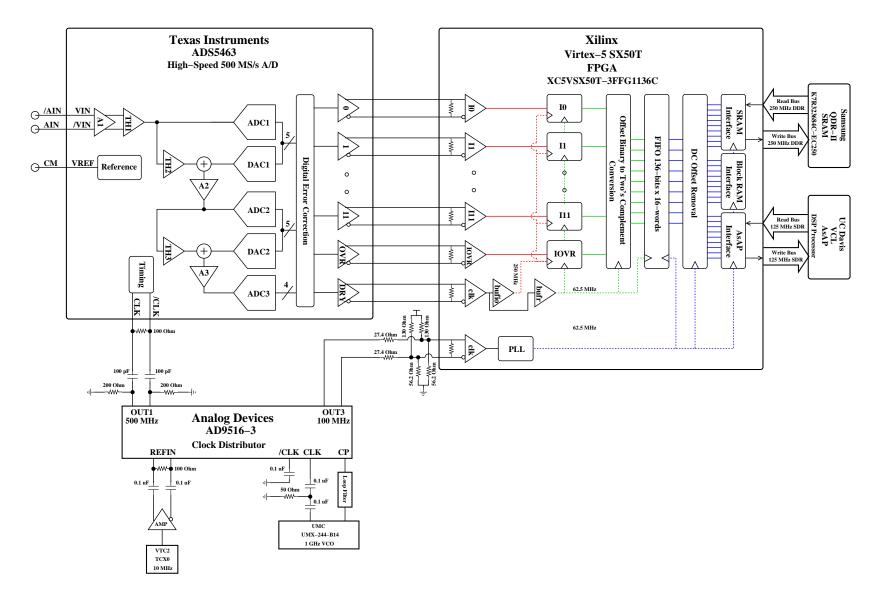

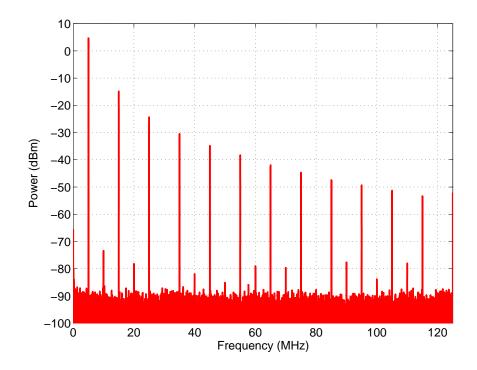

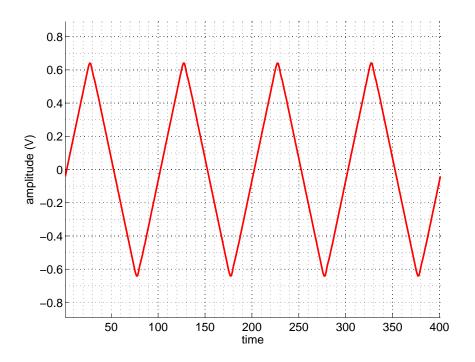

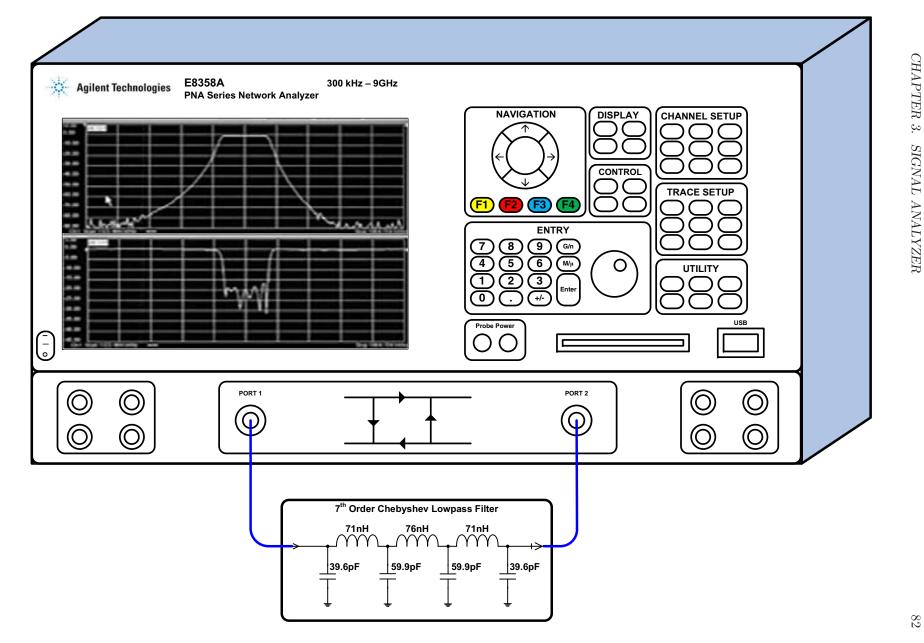

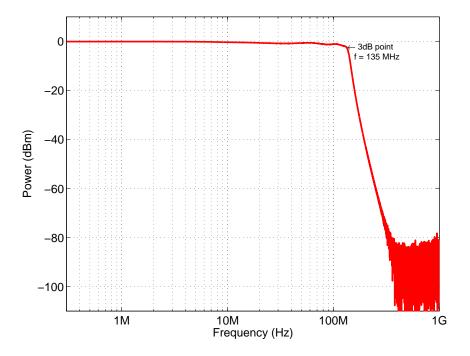

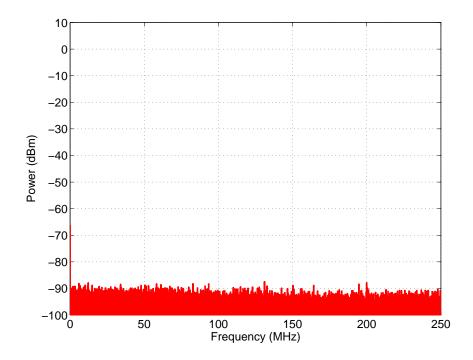

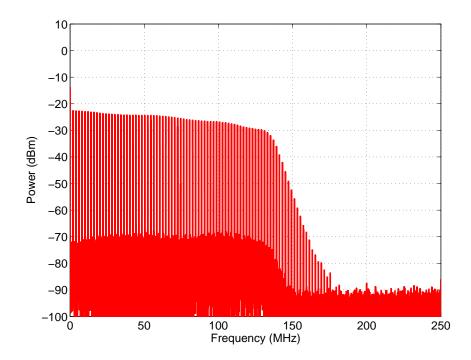

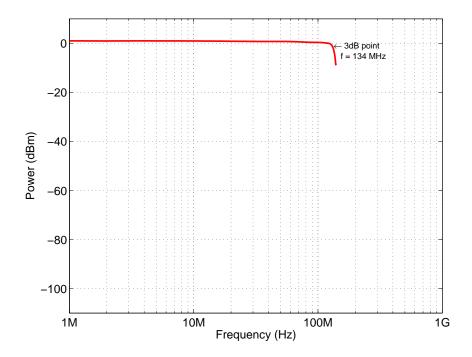

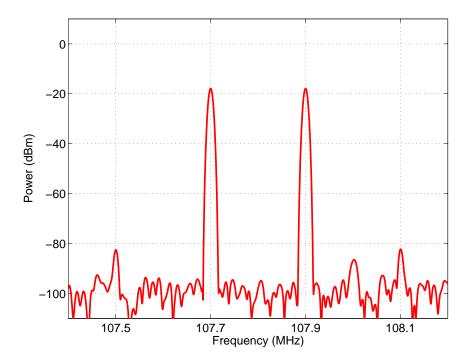

Testing complex digital signal processors (DSPs) requires a development platform with sufficient signal bandwidth and system performance to fully exercise the DSP. Without a development platform, verification of DSPs would be limited to monitoring test output signals for an indication of performance and successful operation. In addition, a development platform with high-speed analog input and output interfaces to the DSP system allows it to be used directly in many sophisticated real-time applications. Presented here is a 334-processor development platform for testing of the Asynchronous Array of Simple Processors (AsAP). This platform, known as the General Purpose Instrument, is capable of generating and analyzing baseband signals. The General Purpose Instrument simplifies the testing and characterization of the AsAP processor when performing real world DSP tasks. The General Purpose Instrument is a flexible platform capable of targeting a wide variety of applications, such as signal generation and signal analysis, and includes: a 12-bit, 500 MS/s analog-to-digital converter (ADC) input, a dual-channel, 16-bit, 1 GS/s digital-to-analog converter (DAC) output, a Xilinx Virtex-5 SX50T data path field programmable gate array (FPGA), a Xilinx Spartan-3A XC3S1400A control FPGA, a 36-Mbit QDR-II static random access memory (SRAM), a 2 GB DDR2 synchronous dynamic random access memory (SDRAM), a 512 Mbit DDR SDRAM, and two 2 GB microSD cards. The signal analyzer input operates with a -3 dB frequency of 134 MHz, and has a noise floor of -98 dBm. The signal source output operates with a -3 dB frequency of 138 MHz, a spurious-free dynamic range (SFDR) of 68.49 dBc at a power level of -6 dBFS, and a signal-to-noise ratio (SNR) of 101.02 dBc.

## Acknowledgments

First, I would like to thank Professor Baas for his guidance and support throughout my years at UC Davis. I would also like to thank Professor Ford and Professor Knoesen for their time in reviewing my thesis.

I'd like to thank everyone that contributed to the design of the measurement board. Application engineers at Texas Instruments, thanks for your help with simulating my signal source and signal analyzer front-end design. Gary Dooley, thanks for teaching me about spectrum analyzer digital IF design. Sam Walker, thank you for your continued support and guidance during the schematic design and PC board layout. Harrell Huckeba, thank you for your help with translating the single-ended anti-alias filter topology to a differential reconstruction filter topology. Robert Uang, thanks for your assistance with the PLL loop-filter design. Patty Walz-Hunter and Jason Thom, thank you for your help with the layout of the measurement board. And thanks to all the members of the VLSI Computation Laboratory.

I'm grateful for the financial support offered by my current and previous employers, including: Centellax, Inc., Agilent Technologies, Inc., Thomson Grass Valley, and Folsom Research.

Finally, I'd like to thank my family. To my parents, thank you for your support and encouragement throughout this time. To my wife, Julie, thank you for putting up with me for the past eight years. It's been a long journey, but it was worth it and I could not have done it without your love and support.

This work was supported in part by the National Science Foundation under Grant No. 0430090 and CAREER Award 0546907 and the Semiconductor Research Corporation under Grant No. 1598.001 and 1659.001.

# Contents

| A  | bstra                            | let                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | iii                                                                                                                                 |  |

|----|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| A  | icknowledgments                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| Li | st of                            | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xii                                                                                                                                 |  |

| Li | st of                            | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\mathbf{x}\mathbf{v}$                                                                                                              |  |

| 1  | <b>Intr</b><br>1.1<br>1.2<br>1.3 | <b>roduction</b> Project Goals         Project Contributions         Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>1</b><br>1<br>1<br>2                                                                                                             |  |

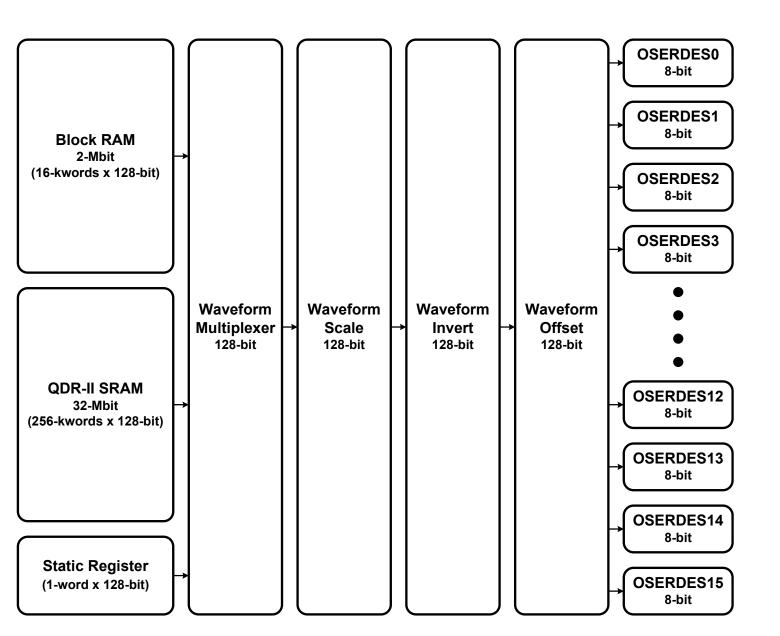

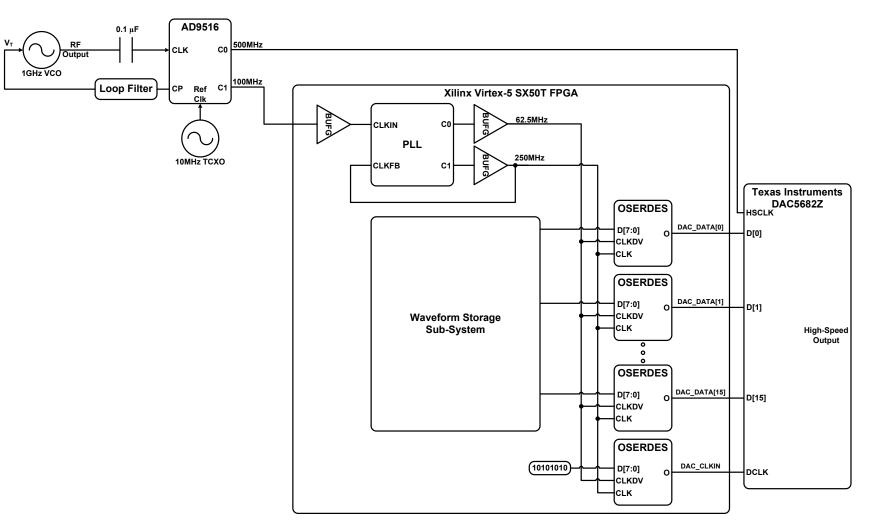

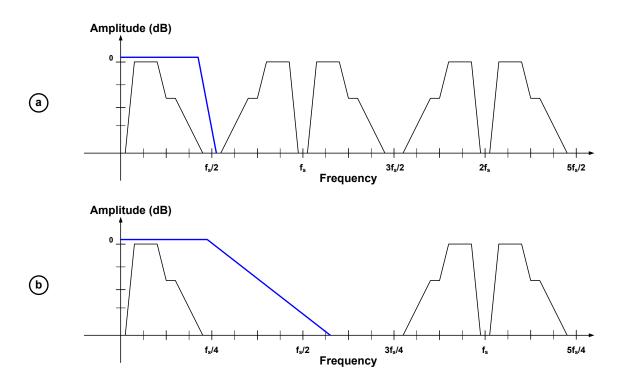

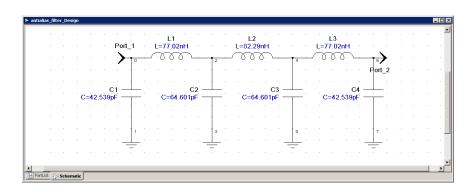

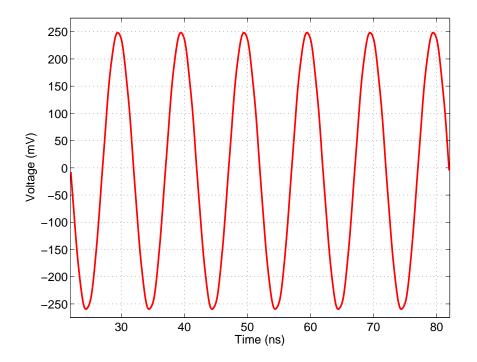

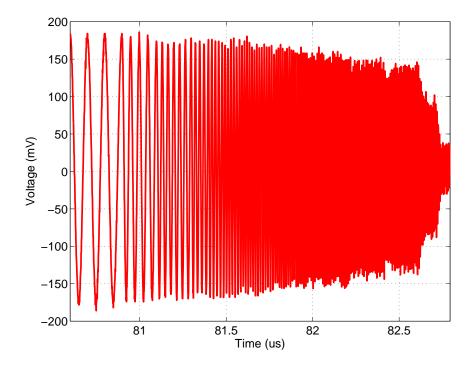

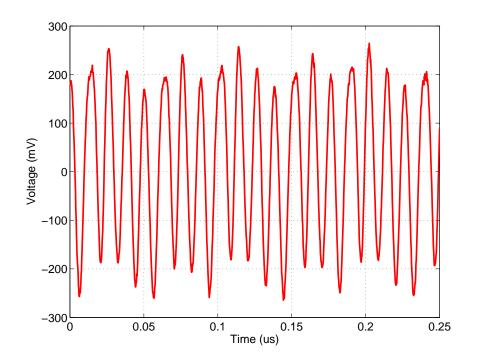

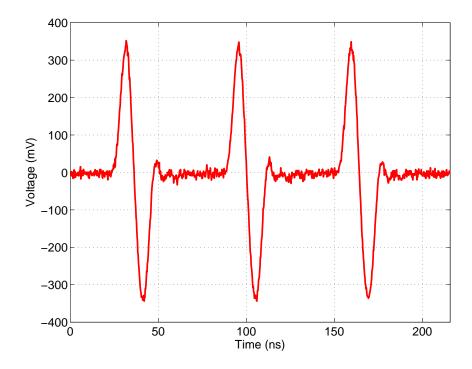

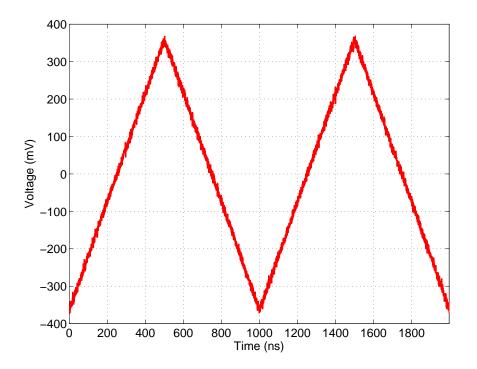

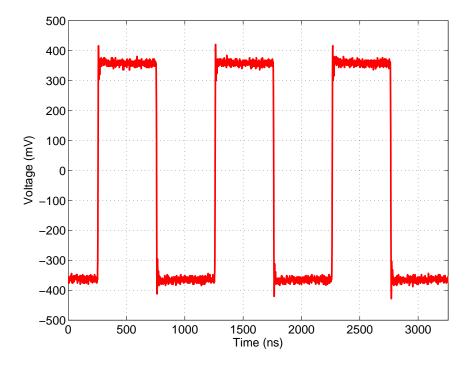

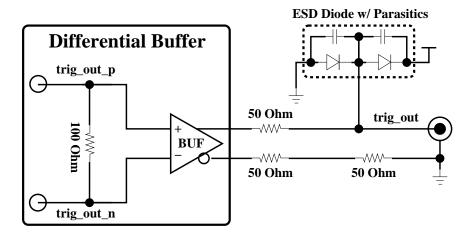

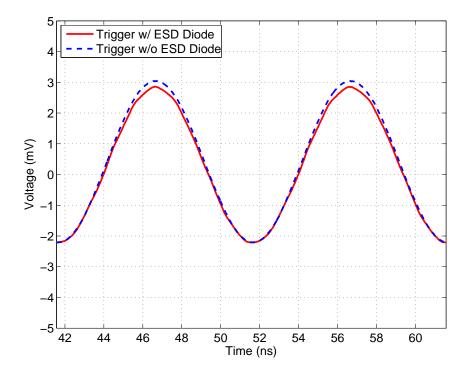

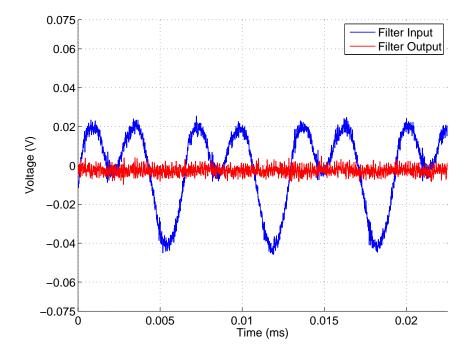

| 2  | Sign<br>2.1<br>2.2               | head Source         Requirements         Design         2.2.1         Digital Signal Processing         2.2.1.1         Waveform Storage and Playback         2.2.1.2         Waveform Scale, Invert, and Offset         2.2.2         High-Speed Digital-to-Analog Converter         2.2.3         Clock Generation and Distribution         2.2.4         Reconstruction Filter         2.2.5         High-Speed Amplifier Output Stage         2.2.6         Waveform Generation Examples         Verification         2.3.1         Time Domain Measurements         2.3.1.2         -3 dB Frequency Measurements Setup         2.3.2.1         -3 dB Frequency Measurements         2.3.2.1         -3 dB Frequency Measurements         2.3.2.1         -3 dB Frequency Measurements         2.3.2.2         Signal-to-Noise Ratio         2.3.2.3         Spurious-Free Dynamic Range         2.3.2.4       Two-tone Third-order Intermodulation Distortion Measurement         2.3.2.5       Frequency Domain Test and Measurement Methodology | $\begin{array}{c} 4\\ 5\\ 7\\ 8\\ 11\\ 12\\ 14\\ 15\\ 17\\ 23\\ 24\\ 30\\ 30\\ 32\\ 34\\ 35\\ 37\\ 39\\ 40\\ 42\\ 45\\ \end{array}$ |  |

| 3  | 2.4<br>Sigr                      | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49<br><b>50</b>                                                                                                                     |  |

| J  | 3.1<br>3.2                       | Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51<br>53<br>54<br>58                                                                                                                |  |

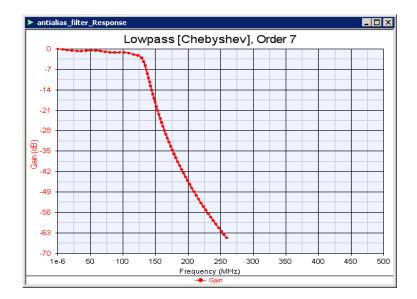

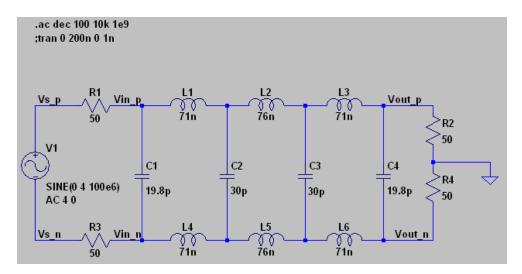

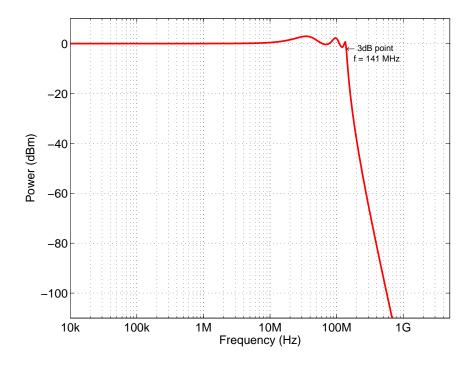

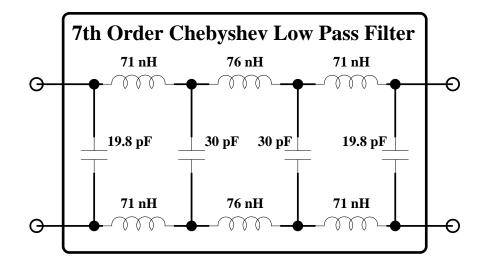

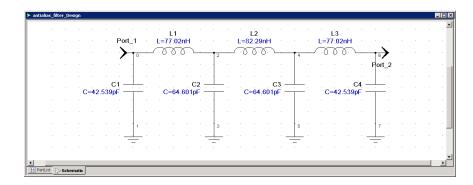

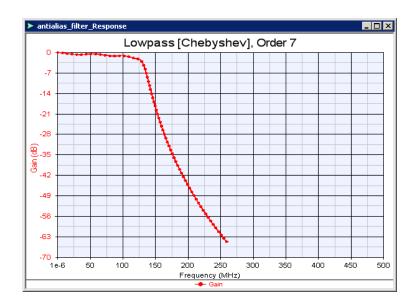

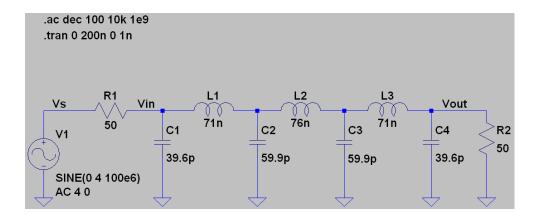

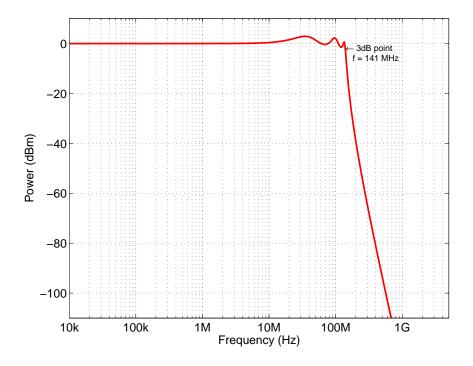

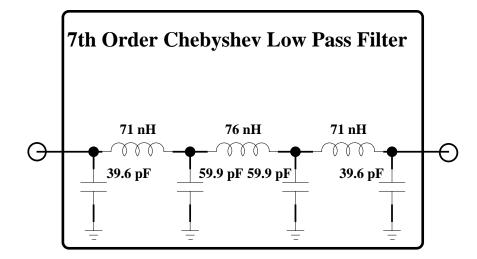

|   |     | 3.2.3   | Anti-Alias Filter Design                                                                                                                     |

|---|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

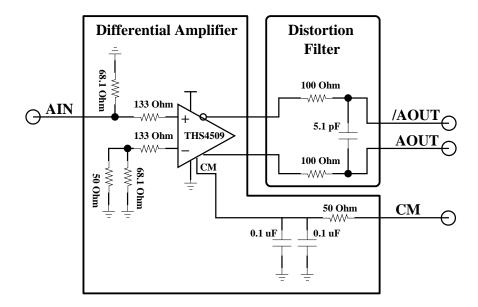

|   |     | 3.2.4   | Differential Amplifier Design                                                                                                                |

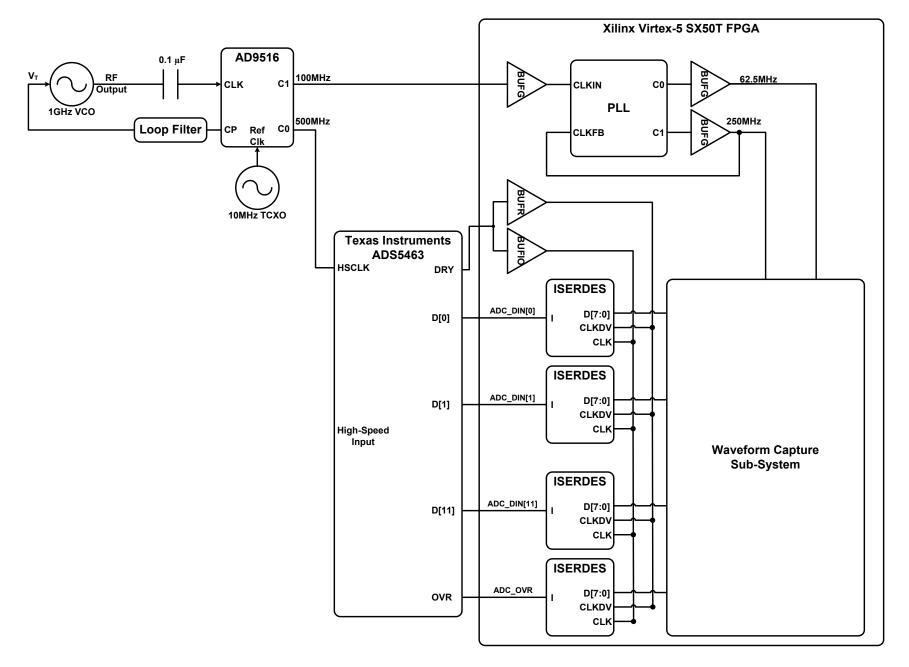

|   |     | 3.2.5   | High-Speed Analog-to-Digital Converter                                                                                                       |

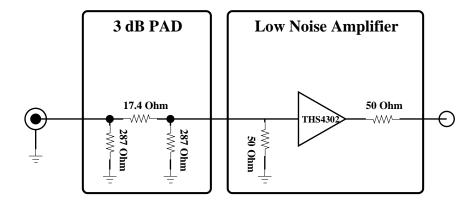

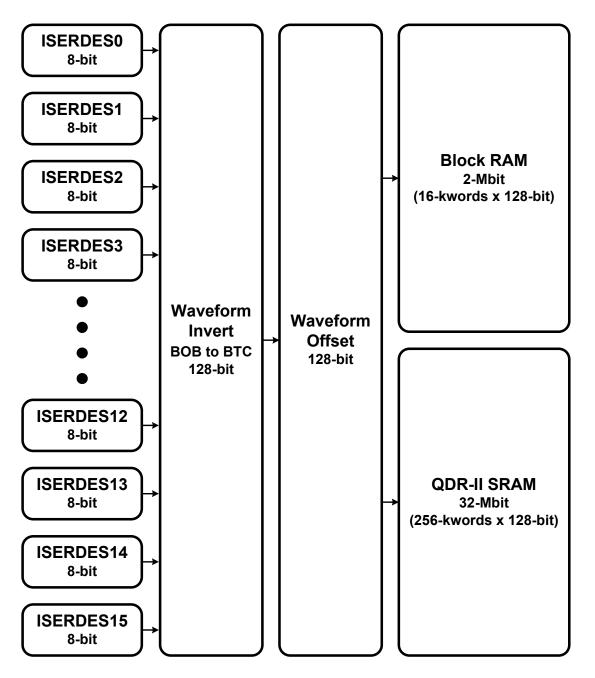

|   |     | 3.2.6   | Digital Signal Processing                                                                                                                    |

|   |     |         | 3.2.6.1 Waveform Capture                                                                                                                     |

|   |     |         | 3.2.6.2 Waveform DC Offset                                                                                                                   |

|   |     | 3.2.7   | Clock Generation and Distribution                                                                                                            |

|   |     | 0.2.1   | 3.2.7.1 High-Speed Clock Generation                                                                                                          |

|   |     |         | ° -                                                                                                                                          |

|   |     | 2.0.0   | 3.2.7.2 High-Speed ADC Data Ready                                                                                                            |

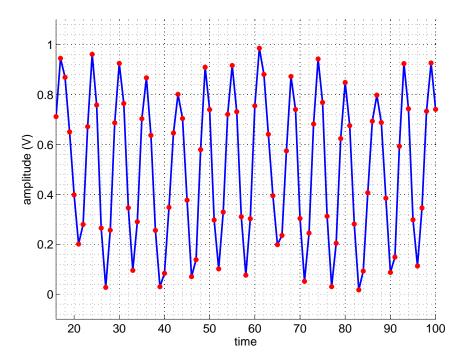

|   | 0.0 | 3.2.8   | Digitized Waveform Examples                                                                                                                  |

|   | 3.3 |         | ation                                                                                                                                        |

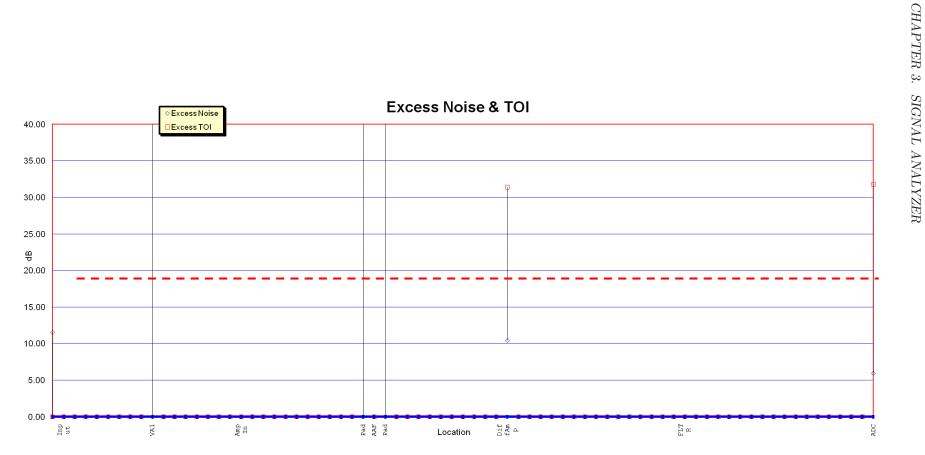

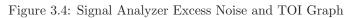

|   |     | 3.3.1   | Frequency Domain Measurements                                                                                                                |

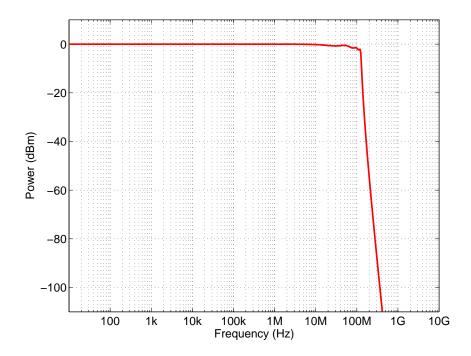

|   |     |         | 3.3.1.1 Anti-Alias Filter Frequency Measurements                                                                                             |

|   |     |         | 3.3.1.2 Receiver Characterization                                                                                                            |

|   | 3.4 | Specifi | cations                                                                                                                                      |

|   |     |         |                                                                                                                                              |

| 4 | Mea |         | ent Board 94                                                                                                                                 |

|   | 4.1 | Requi   | ements                                                                                                                                       |

|   |     | 4.1.1   | Power Distribution System                                                                                                                    |

|   |     | 4.1.2   | Component Placement                                                                                                                          |

|   |     | 4.1.3   | Layout Strategy                                                                                                                              |

|   |     | 4.1.4   | Radio Frequency and Electromagnetic Interference                                                                                             |

|   |     | 4.1.5   | Signal Integrity                                                                                                                             |

|   | 4.2 |         | 98                                                                                                                                           |

|   |     | 4.2.1   | Printed Circuit Board Construction                                                                                                           |

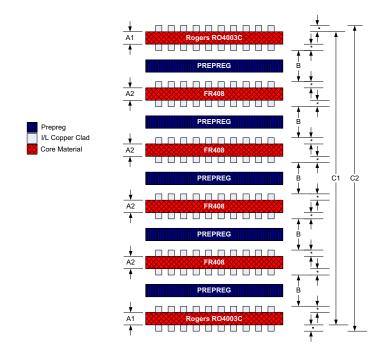

|   |     | 1.2.1   | 4.2.1.1 Printed Circuit Board Stackup                                                                                                        |

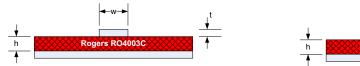

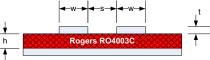

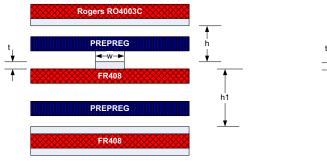

|   |     |         | 4.2.1.2 Transmission Line Structures                                                                                                         |

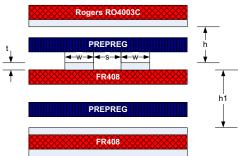

|   |     | 4.2.2   | Component Placement                                                                                                                          |

|   |     | 4.2.2   | 4.2.2.1 Printed Circuit Board Pre-Placement                                                                                                  |

|   |     |         |                                                                                                                                              |

|   |     |         |                                                                                                                                              |

|   |     |         | 4.2.2.3 Decoupling Capacitor Placement Planning 104                                                                                          |

|   |     |         | 4.2.2.4 High-Speed Device Considerations                                                                                                     |

|   |     | 4.2.3   | Printed Circuit Board Layout                                                                                                                 |

|   |     |         | 4.2.3.1 Routing Groups                                                                                                                       |

|   |     |         | 4.2.3.2 Planning for Power and Ground Planes                                                                                                 |

|   |     |         | 4.2.3.3 Net Type Assignments 111                                                                                                             |

|   |     |         | 4.2.3.4 Digital Signal Routing                                                                                                               |

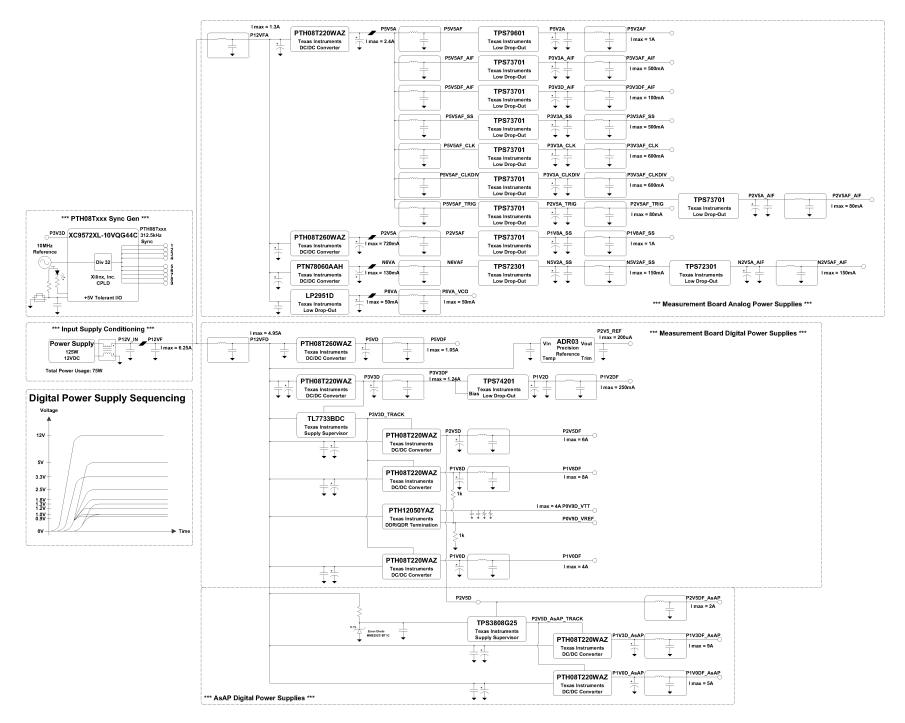

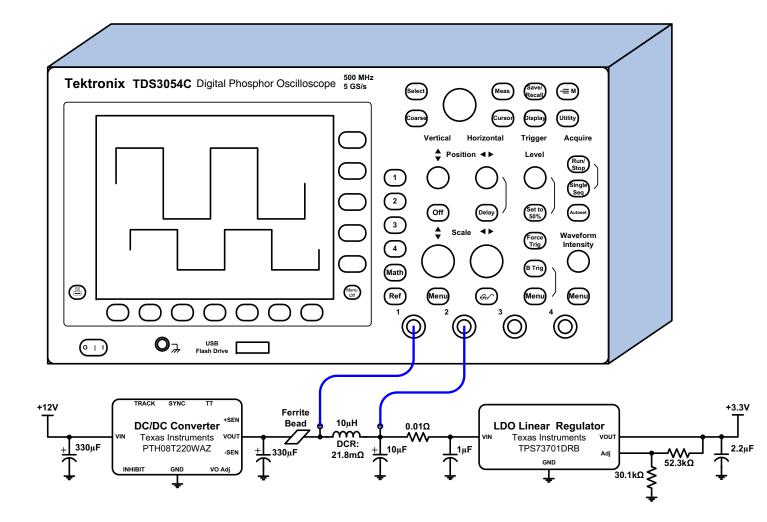

|   |     | 4.2.4   | Power Supply Design                                                                                                                          |

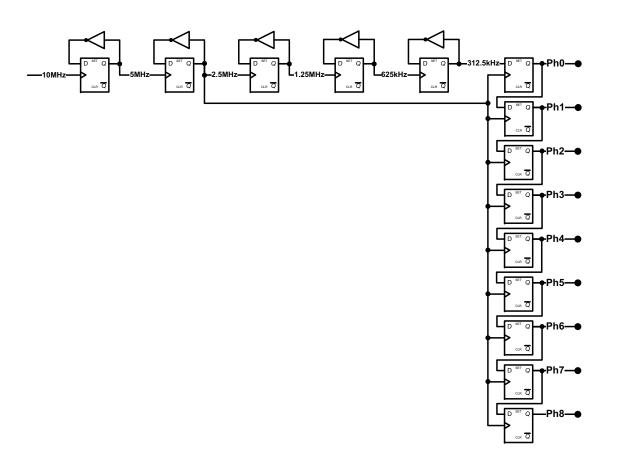

|   |     |         | 4.2.4.1 Power Supply Synchronization                                                                                                         |

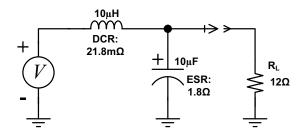

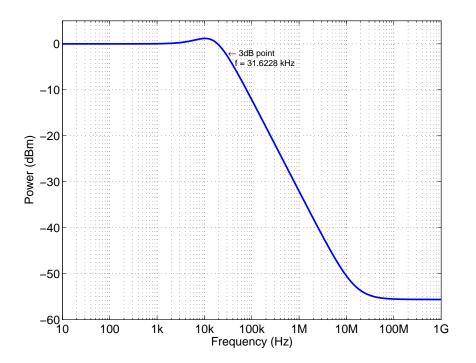

|   |     |         | 4.2.4.2 Power Supply Filtering 119                                                                                                           |

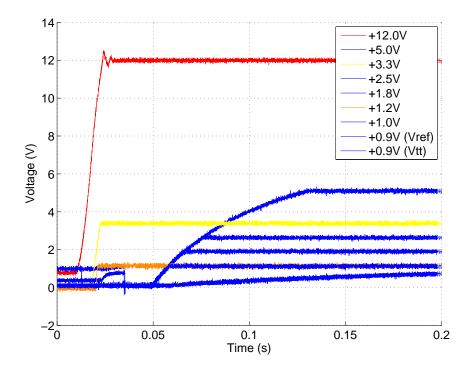

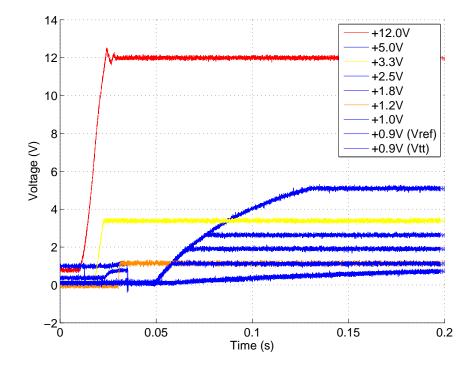

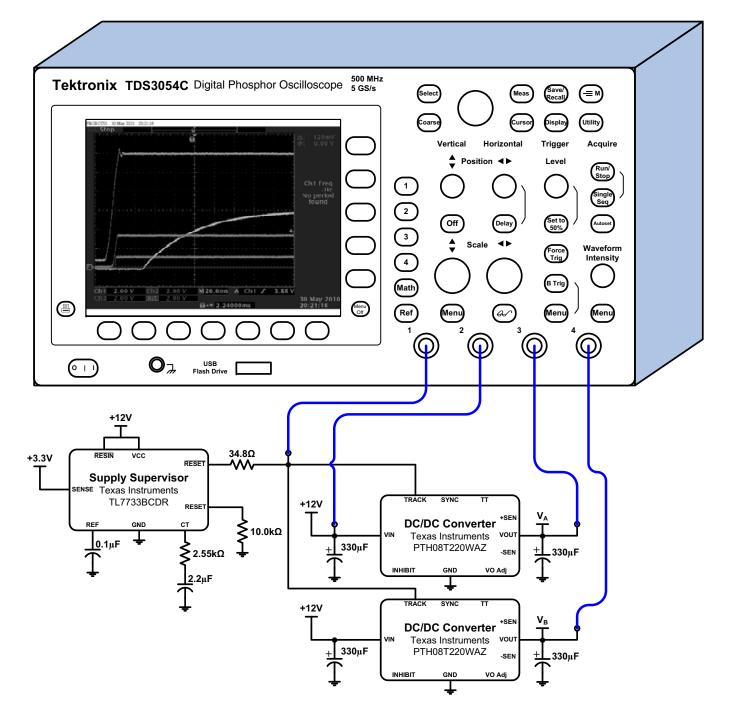

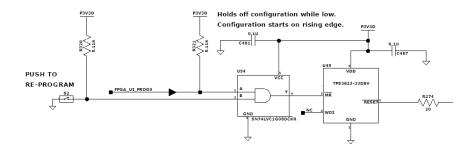

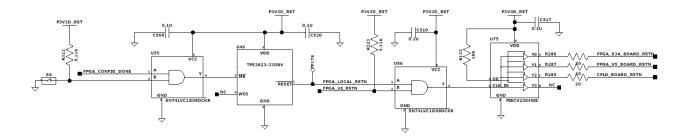

|   |     |         | 4.2.4.3 Power Supply Sequencing                                                                                                              |

|   |     |         | 4.2.4.4 Power Consumption                                                                                                                    |

|   | 4.3 | Verific | ation $\ldots \ldots \ldots$ |

|   |     | 4.3.1   | Printed Circuit Board Turn-on                                                                                                                |

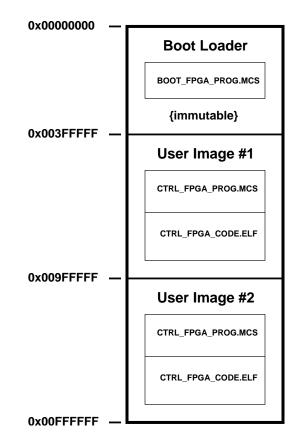

|   |     | 1.0.1   | 4.3.1.1 Data Path FPGA Configuration Modification                                                                                            |

|   |     |         | 4.3.1.2 High-Speed Digital-to-Analog Converter Modification                                                                                  |

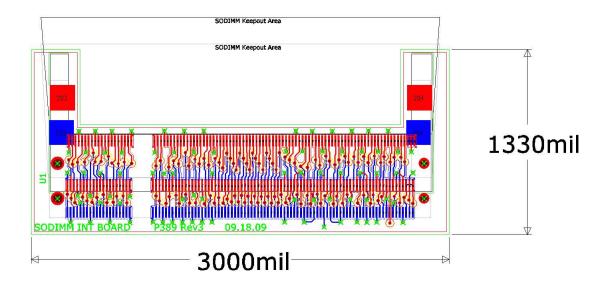

|   |     |         | 4.3.1.3 DDR2 SDRAM SODIMM Socket Modification                                                                                                |

|   |     |         |                                                                                                                                              |

|   |     |         |                                                                                                                                              |

|   |     |         | 4.3.1.5 Power Supply Filtering                                                                                                               |

|   |     |         | 4.3.1.6 Power Supply Sequencing                                                                                                              |

|   |     |         | 4.3.1.7 Power Supply Consumption                                                                                                             |

|   |     |         |                                                                                                                                              |

5 Future Work and Conclusion

141

| $\mathbf{A}$ | Waveform Generation and Play Back           | 143        |

|--------------|---------------------------------------------|------------|

|              | A.1 Waveform File Format                    | . 144      |

|              | A.1.1 Filename Support                      |            |

|              | A.1.2 File Header                           | . 145      |

|              | A.1.3 Sample Waveform File                  |            |

|              | A.1. $3.1$ File Data                        |            |

|              | A.2 Waveform Replication                    |            |

|              | A.3 Waveform Parameters                     |            |

|              | A.3.1 Waveform Bit Length                   |            |

|              | A.3.2 Waveform Memory Stop Address          |            |

|              | A.3.3 Waveform Mark Density                 |            |

|              | A.4 Waveform Generation                     |            |

|              | A.4.1 Sinusoid Waveform Generation          |            |

|              | A.4.2 Ramp Waveform Generation              |            |

|              | A.4.3 Square Waveform Generation            |            |

|              | A.4.4 Waveform Generation Automation        |            |

|              | A.5 Waveform Play Back                      |            |

|              |                                             | . 100      |

| $\mathbf{B}$ | Waveform Conversion Perl Script             | 166        |

|              | B.1 NAME                                    | . 166      |

|              | B.2 SYNOPSIS                                | . 166      |

|              | B.3 OPTIONS                                 | . 166      |

|              | B.4 DESCRIPTION                             | . 167      |

|              | B.5 SUBROUTINES                             |            |

|              | B.6 CODE                                    | . 171      |

| С            | Square Waveform Generation Perl Script      | 194        |

| U            | C.1 NAME                                    |            |

|              | C.2 SYNOPSIS                                |            |

|              | C.3 OPTIONS                                 |            |

|              | C.4 DESCRIPTION                             |            |

|              | C.5 SUBROUTINES                             |            |

|              | C.6 CODE                                    |            |

|              |                                             | . 101      |

| D            | Ramp Waveform Generation Perl Script        | <b>209</b> |

|              | D.1 NAME                                    |            |

|              | D.2 SYNOPSIS                                |            |

|              | D.3 OPTIONS                                 |            |

|              | D.4 DESCRIPTION                             |            |

|              | D.5 SUBROUTINES                             |            |

|              | D.6 CODE                                    | . 212      |

| Е            | ADC Waveform Capture Conversion Perl Script | 224        |

|              | E.1 NAME                                    |            |

|              | E.2 SYNOPSIS                                |            |

|              | E.3 OPTIONS                                 |            |

|              | E.4 DESCRIPTION                             |            |

|              | E.5 SUBROUTINES                             | -          |

|              | E.6 CODE                                    |            |

|              |                                             | •          |

| $\mathbf{F}$ |      |                                                                  | 43  |

|--------------|------|------------------------------------------------------------------|-----|

|              | F.1  | DDR SDRAM Routing Constraints                                    | 243 |

|              | F.2  | DDR2 SDRAM SODIMM Routing Constraints                            | 246 |

|              | F.3  | QDR-II SRAM Routing Constraints                                  | 248 |

|              | F.4  | High-Speed ADC Routing Constraints                               | 249 |

|              | F.5  |                                                                  | 250 |

|              | F.6  |                                                                  | 250 |

| G            | Prii | nted Circuit Board Net Type Assignments 2                        | 52  |

| н            | Dat  | a Path FPGA IODELAY Results 2                                    | 80  |

|              |      |                                                                  | 280 |

|              |      |                                                                  | 290 |

|              |      |                                                                  | 291 |

|              |      |                                                                  | 295 |

|              |      | -                                                                | 299 |

|              |      |                                                                  | 301 |

|              |      |                                                                  |     |

| Ι            |      | 0                                                                | 03  |

|              | I.1  |                                                                  | 304 |

|              |      |                                                                  | 804 |

|              |      | 0 ,                                                              | 804 |

|              |      | i O /                                                            | 805 |

|              |      | 1 0 /                                                            | 806 |

|              |      | 1 0 /                                                            | 808 |

|              |      |                                                                  | 809 |

|              |      |                                                                  | 810 |

|              |      |                                                                  | 311 |

|              | то   | 0                                                                | 811 |

|              | I.2  | ,                                                                | 812 |

|              |      | 0                                                                | 812 |

|              | то   | 0                                                                | 812 |

|              | I.3  |                                                                  | 313 |

|              |      |                                                                  | 313 |

|              |      |                                                                  | 313 |

|              |      |                                                                  | 814 |

|              |      |                                                                  | 314 |

|              |      |                                                                  | 315 |

|              |      | •                                                                | 815 |

|              |      |                                                                  | 816 |

|              |      |                                                                  | 816 |

|              |      |                                                                  | 817 |

|              |      |                                                                  | 817 |

|              |      |                                                                  | 318 |

|              |      |                                                                  | 818 |

|              |      |                                                                  | 819 |

|              |      |                                                                  | 819 |

|              |      |                                                                  | 820 |

|              |      |                                                                  | 821 |

|              |      |                                                                  | 322 |

|              |      | I.3.18 Playback RAM Write Trigger Data Register, Address: 0x0322 | 322 |

|              |      | I.3.19 Capture RAM Read Control Register, Address: 0x0324        | 323 |

|              |      | I.3.20 Capture RAM Read Address Register, Address: 0x0326 3      | 323 |

|              |      |                                                                  | 324 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.0.4      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     | 1.3.22 Capture RAM Write Stop Address Register, Address: 0x032A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|     | I O )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 325        |

|     | 1.3.24 Capture RAM Write Maximum Address Register, Address: 0x032E 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|     | I.3.25       Capture RAM Read Data 0 Register, Address: 0x0330       0x0330 |            |

|     | I.3.26 Capture RAM Read Data 1 Register, Address: 0x0332                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|     | 1.3.27 Capture RAM Read Data 2 Register, Address: 0x0334                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|     | I.3.28 Capture RAM Read Data 3 Register, Address: 0x0336                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|     | I.3.29 Capture RAM Read Data 4 Register, Address: 0x0338                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 328        |

|     | I.3.30 Capture RAM Read Data 5 Register, Address: 0x033A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 328        |

|     | I.3.31 Capture RAM Read Data 6 Register, Address: 0x033C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 329        |

|     | I.3.32 Capture RAM Read Data 7 Register, Address: 0x033E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 329        |

|     | 1.3.33 Capture RAM Read Data 8 Register, Address: 0x0340                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 330        |

|     | 1.3.34 Capture RAM Read Status Register, Address: 0x0342                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 330        |

|     | 1.3.35 Playback RAM FIFO Read Count Register, Address: 0x0344                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 331        |

|     | 1.3.36 Playback Block RAM Write Control Register, Address: 0x0380                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 331        |

|     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 332        |

|     | 1.3.38 Playback Block RAM Write Data 0 Register, Address: 0x0384                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|     | I.3.39 Playback Block RAM Write Data 1 Register, Address: 0x0386                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|     | I.3.40 Playback Block RAM Write Data 2 Register, Address: 0x0388                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|     | I.3.41 Playback Block RAM Write Data 3 Register, Address: 0x038A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|     | I.3.42 Playback Block RAM Read Control Register, Address: 0x038C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 335        |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 335        |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 336        |

|     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 336        |

|     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 337        |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 337        |

|     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 338        |

|     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 338        |

|     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 339        |

|     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 339<br>339 |

|     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

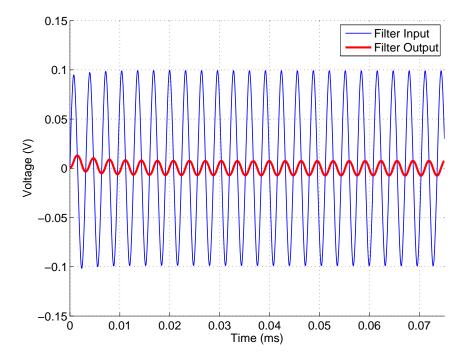

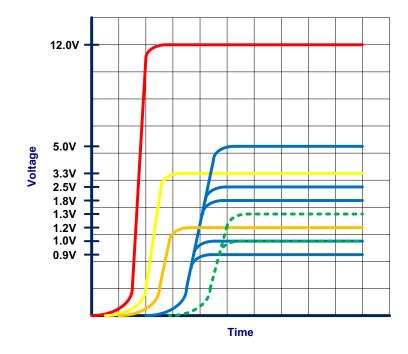

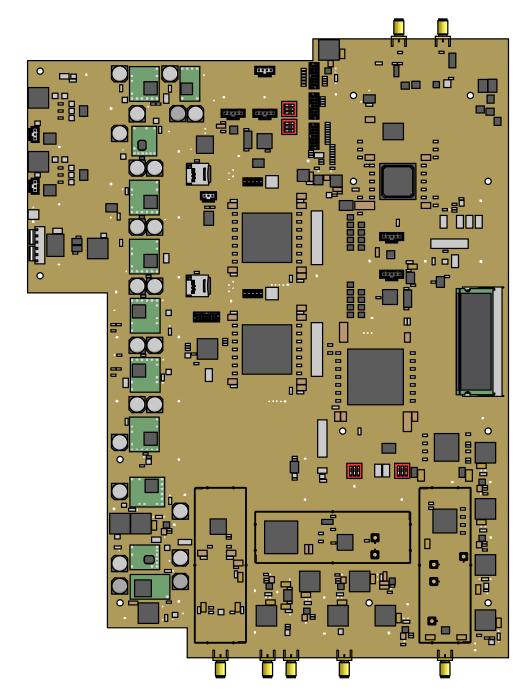

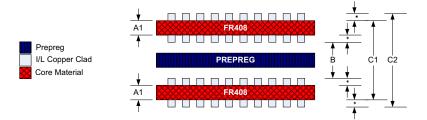

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 340        |