Documents

Poster

A Generator of Memory-Based, Runtime-Reconfigurable 2n3m5k FFT Engines

- Citation Author(s):

- Submitted by:

- Angie Wang

- Last updated:

- 24 March 2016 - 1:53pm

- Document Type:

- Poster

- Document Year:

- 2016

- Event:

- Presenters:

- Angie Wang

- Paper Code:

- DISPS-P1.7

- Categories:

- Log in to post comments

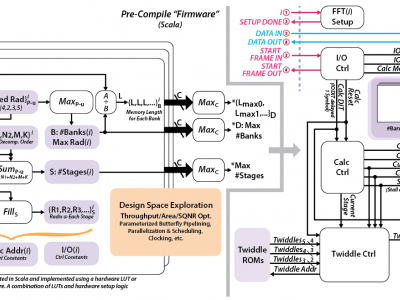

Runtime-reconfigurable, mixed-radix FFT/IFFT engines are essential for modern wireless communication systems. To comply with varying standards requirements, these engines are customized for each modem. The Chisel hardware construction language has been used in this work to create a generator of runtime-reconfigurable 2n3m5k(7l...) FFT engines targeting software-defined radios (SDR) for modern communications, but with flexibility to support a wide range of applications. The generator uses a conflict-free, in-place, multi-bank SRAM design, and exploits the duality of decimation-in-frequency (DIF) and decimation-in-time (DIT) FFTs to support continuous data flow with only 2N memory blocks (for a given N-point FFT). DFT decomposition using the prime-factor algorithm (PFA) followed by the Cooley-Tukey algorithm (CTA) reduces twiddle ROM sizes. A programmable Winograd’s Fourier Transform (WFTA) butterfly supporting radix-2/3/4/5/7 operations reuses radix-7 hardware to support reconfigurability with minimal area penalty.