- Read more about SLAP: A Split Latency Adaptive VLIW Pipeline Architecture which enables on-the-fly Variable SIMD Vector Length

- Log in to post comments

Over the last decade the relative latency of access to shared memory by multicore increased as wire resistance dominated latency and low wire density layout pushed multi-port memories farther away from their ports. Various techniques were deployed to improve average memory access latencies, such as speculative pre-fetching and branch-prediction, often leading to high variance in execution time which is unacceptable in real-time systems. Smart DMAs can be used

- Categories:

30 Views

30 Views

- Read more about A Generator of Memory-Based, Runtime-Reconfigurable 2n3m5k FFT Engines

- Log in to post comments

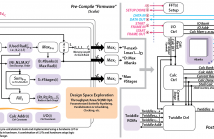

Runtime-reconfigurable, mixed-radix FFT/IFFT engines are essential for modern wireless communication systems. To comply with varying standards requirements, these engines are customized for each modem. The Chisel hardware construction language has been used in this work to create a generator of runtime-reconfigurable 2n3m5k(7l...) FFT engines targeting software-defined radios (SDR) for modern communications, but with flexibility to support a wide range of applications.

- Categories:

45 Views

45 Views