Documents

Poster

Visualization of SLAM Backend Accelerator

- DOI:

- 10.60864/sdm3-wa24

- Citation Author(s):

- Submitted by:

- xavante erickson

- Last updated:

- 6 June 2024 - 10:54am

- Document Type:

- Poster

- Document Year:

- 2024

- Event:

- Presenters:

- Xavante Erickson

- Paper Code:

- 8850

- Categories:

- Log in to post comments

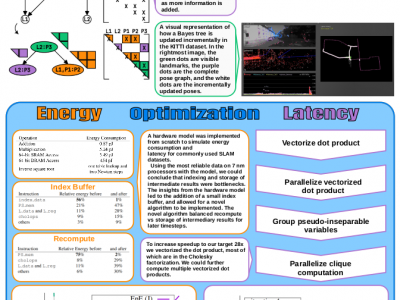

This research aims to develop energy-efficient hardware accelerators for Simultaneous Location And Mapping (SLAM) back end applications by employing algorithm-hardware co-design. Utilizing the iSAM2 algorithm, which uses graphical modeling to solve iterative Gauss-Newton problems, we continuously update maps by incorporating solutions from previous iterations or timesteps. We address the performance bottleneck arising from memory writes of intermediate results by modifying the original algorithm. Additionally, we analyze the algorithm's parallelizability to meet latency demands. These hardware accelerators are designed as Intellectual Property (IP) blocks, suitable for integration into custom Systems-on-Chip (SoC). We evaluate the design using both holistic and block-level metrics, focusing on latency and energy efficiency. This work has implications for energy-constrained devices like drones and Extended Reality (XR) devices.